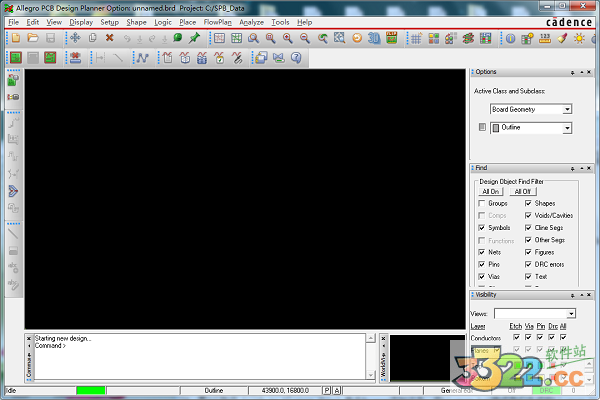

cadence allegro16.5破解版,cadence allegro是铿腾电子推出的一款高速电路板设计与仿真软件,主要用于PCB设计布线。与其他同类型的程序相比,cadence allegro最大的一个功能就是拥有着最为先进的PCB编辑器,PCB编辑器能为用户分享最为强大的PCB编辑功能,用户可以让它进行自动化的编辑操作,以此来配合用户的操作。同时PCB编辑器可以将用户布线的效率最大化,其利用图形化以及实时化的和任意角度的推挤布线,让用户可以自由的进行推挤优先、环绕优先或仅环绕等布线模式的选择,其中推挤优先模式可以让用户以最大的速度去建造出最合适的互联路径,在这过程中PCB编辑器的布线器系统就会自动帮用户解决动态推挤障碍,而布线也会自动跳跃障碍,如引脚或导孔。新版cadence allegro16.5除了保持旧版的强大功能和稳定的设计环境之外,还额外增加和优化了许多的功能。例如cadence allegro16.5新增了两个约束,用于嵌入过程中的自检,以此来为用户的设计添加更为深层次的保障。同时在手动放置中,现在用户可以在cadence allegro16.5自由选择嵌入的器件,而且在这过程中元件也会自动放入到内层中,在这之后,用户在选择器件的时候,就可以右键改变该嵌入层,使之只有可以嵌入的层才会出现。除此之外,cadence allegro16.5最大的一个改动就是用户当单击状态栏的某个区域的时候就是实现相关的某种功能。例如在状态栏点选模式领域,就可以切换到其它模式。当然啦新版cadence allegro16.5还有着诸多新的实用功能,包括在动态铜,静态铜的显示上分享了不同的显示效果、新增加了动态层面的显示功能等等。知识兔小编就不在这里一一介绍了,用户自行下载cadence allegro16.5破解版探索吧。

16.5破解版安装教程

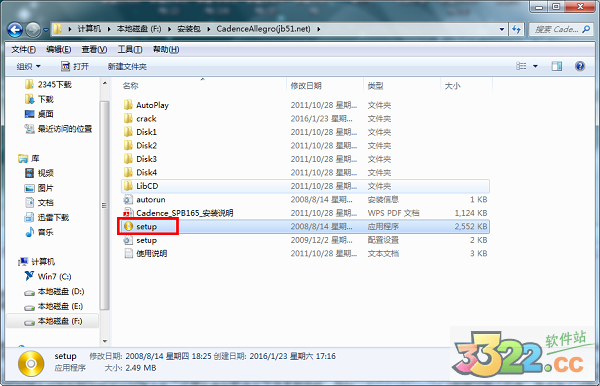

1、解压安装包,然后点击“setup.exe”开始正式的安装

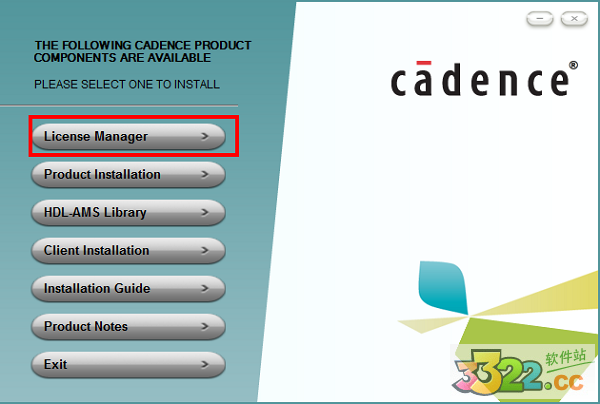

2、这里先选择license manager进行安装

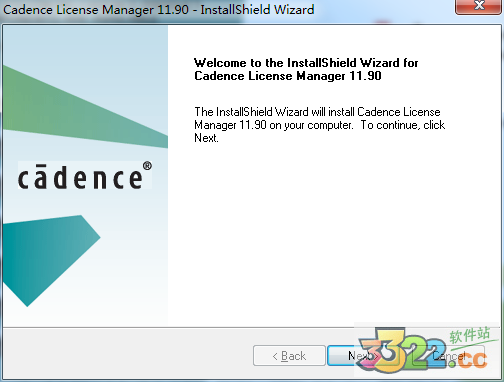

3、点击“next”

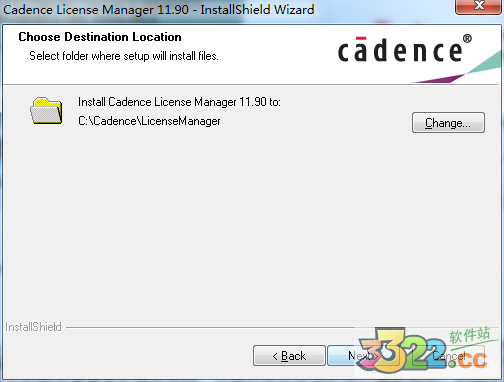

4、默认安装,直到选择安装的路径,这里无需注意什么,建议用户最好安装到自己经常使用的系统盘的文件夹上面,以此方便破解

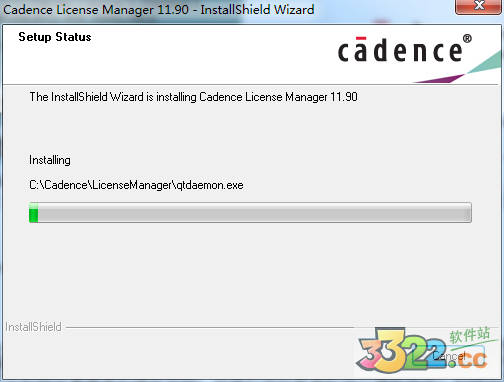

5、安装中......

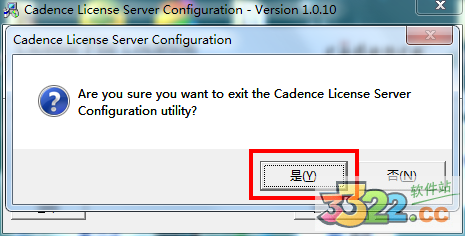

6、安装的过程中会跳出license选择,这里用户直接点击cancel

7、然后点击“是”

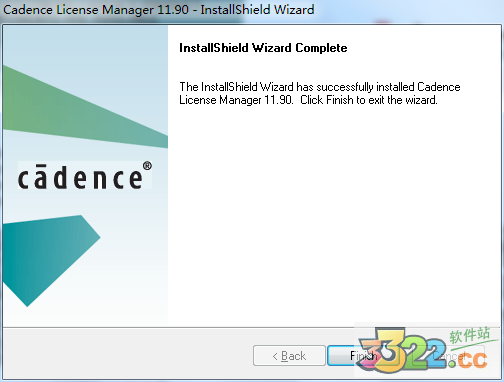

8、安装完成

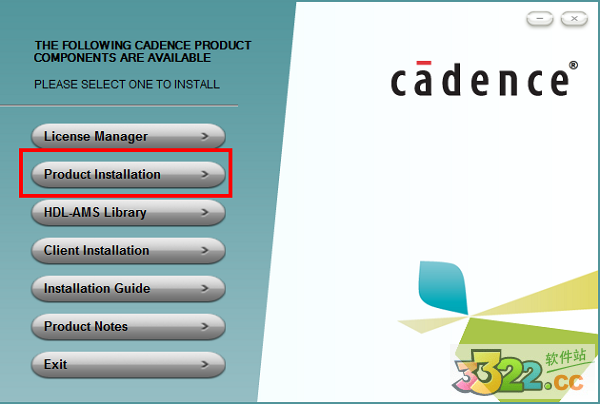

9、回到打开程序时的初始界面,然后点击product installation进行安装

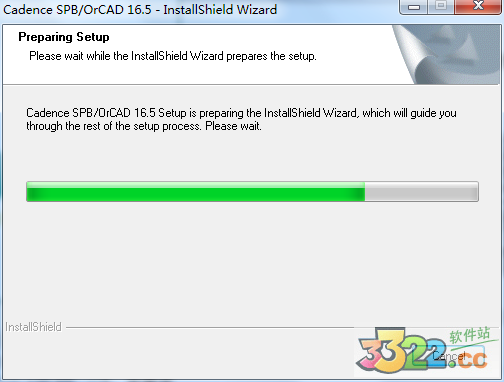

10、解压中.....

11、然后点击“next”

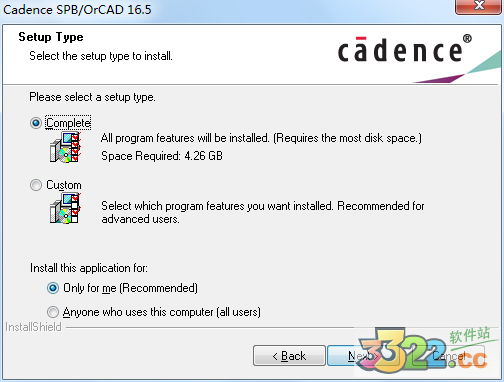

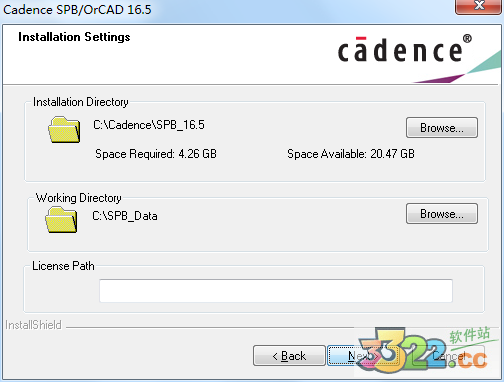

12、默认安装,然后安装到如下图,这里建议默认,如果用户熟悉程序那么可自定义安装

13、选择安装路径,这里用户随意选择即可,但是记住一定要记住该文件夹哦,破解的时候要用到

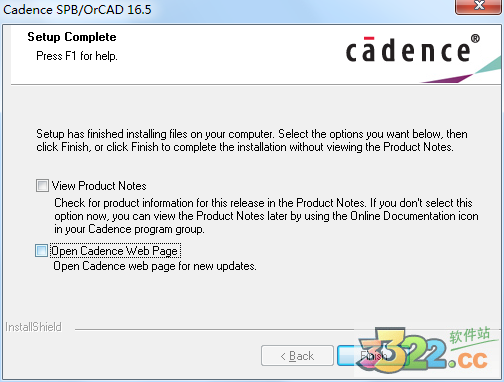

14、直到安装完成.....

16.5破解版破解教程

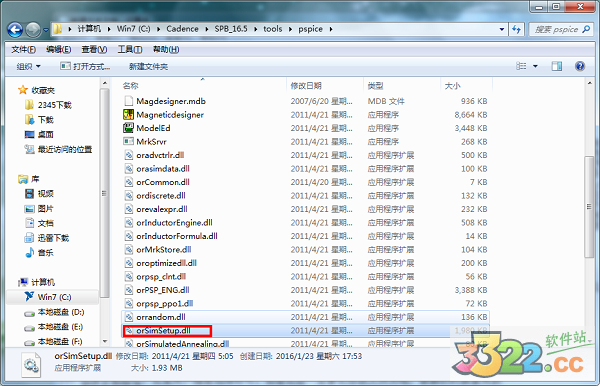

1、把\Cadence\SPB_16.5\tools\pspice文件中的orSimSetup.dll剪切到其他任何地方,否者将不利于破解

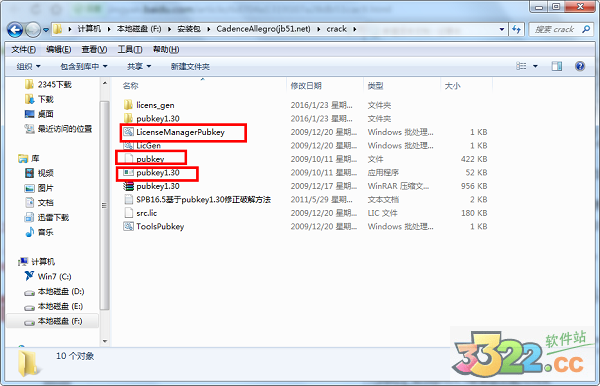

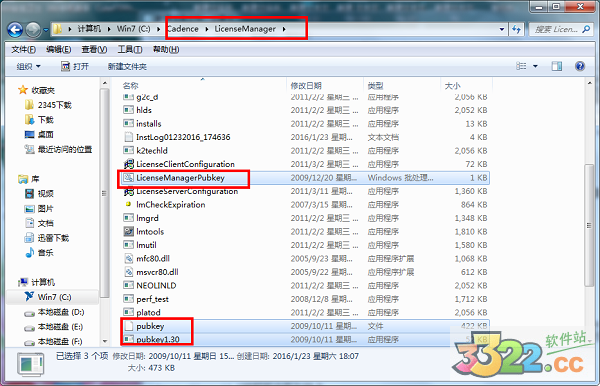

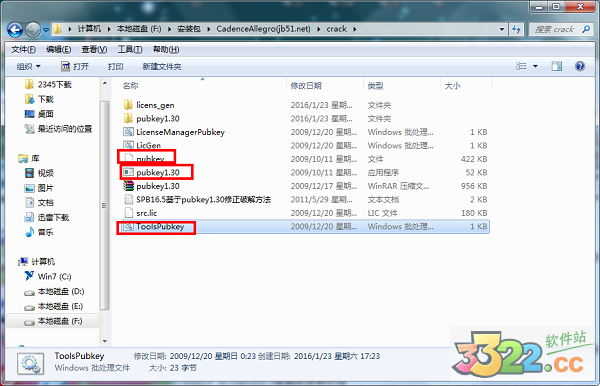

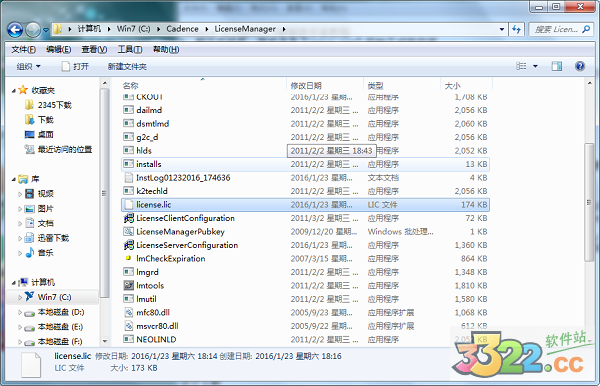

2、打开安装文件中的crack文件,然后将pubkey、pubkey1.30.exe 和lLicenseManagerPubkey.bat放到Cadence\LicenseManage目录下(即安装目录)

3、然后运行LicenseManagerPubkey.bat

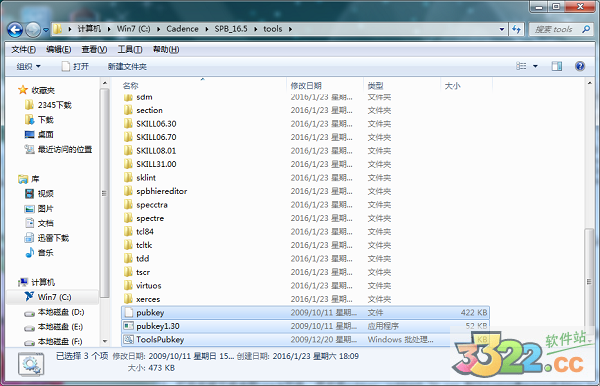

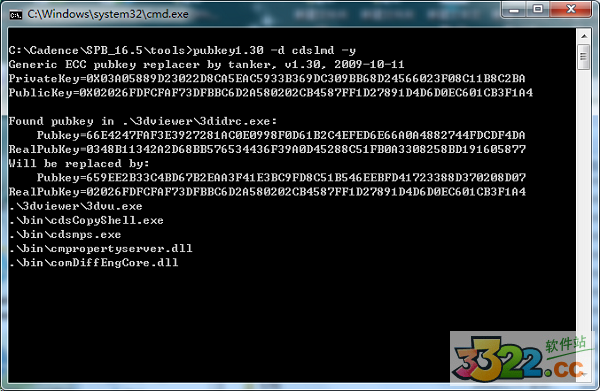

4、打开安装文件中的crack文件,将pubkey、pubkey1.3.exe和ToolsPubkey.bat放到Cadence\SPB_16.5\tools目录下并运行ToolsPubkey.bat

PS:如果运行该文件出现can not open或者是 diff pubkey等字样时不必惊慌,文件还是能够破解的,继续运行下面的步骤

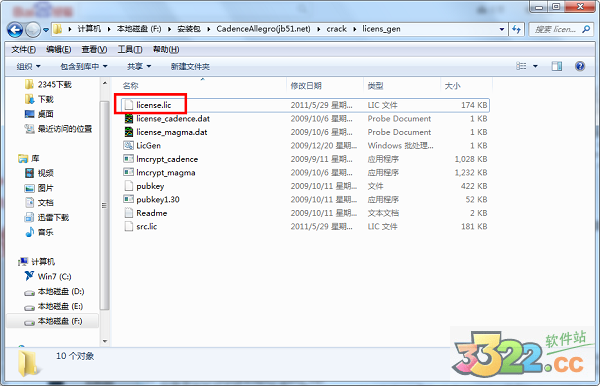

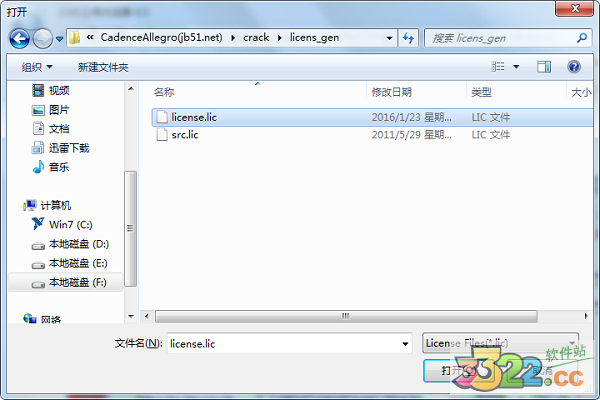

5、删除crack文件下licens_gen下的 license.lic

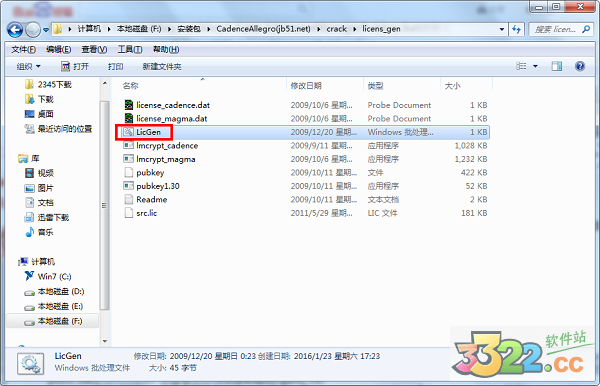

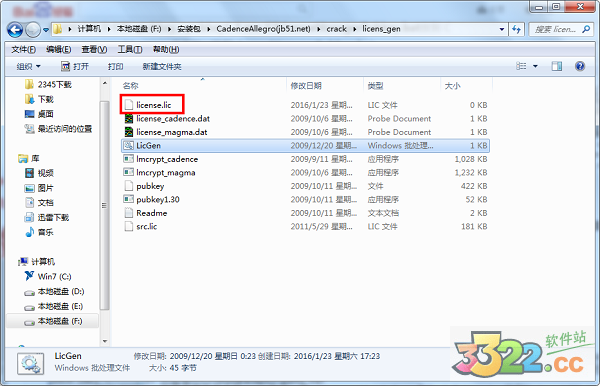

6、点击licgen.bat生成新的license.lic

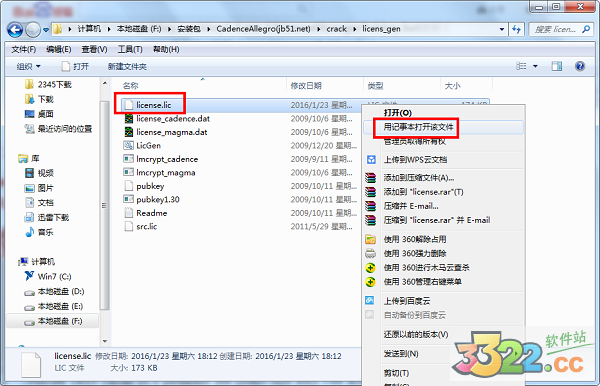

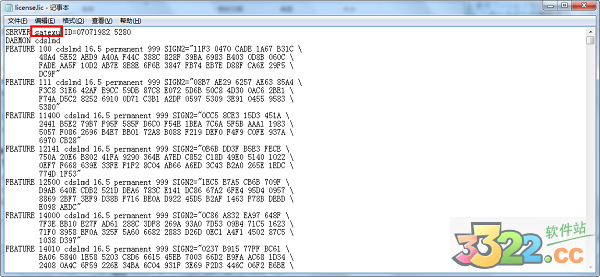

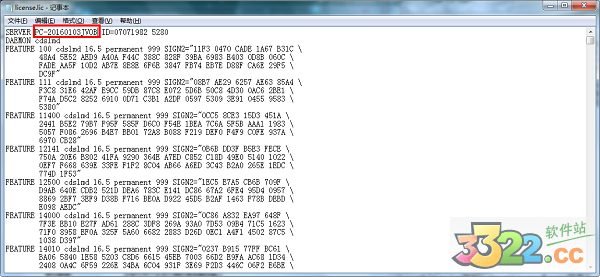

7、要记事本打开新的license.lic

8、将如下图标示的地方修改为自己的计算机名称,然后保存

PS:不知道自己计算机名称的,可以安装以下教程进行操作

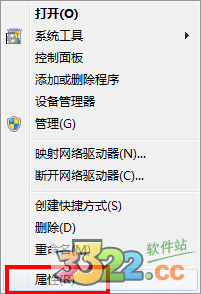

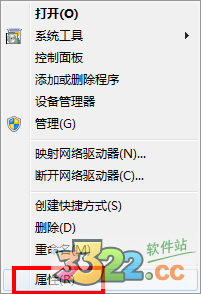

1.鼠标右键点击计算机,然后点击属性

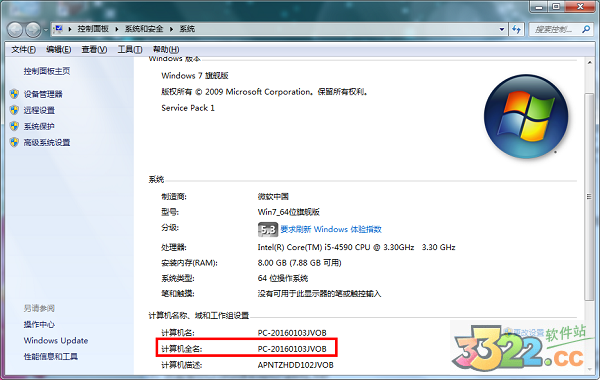

2.找到如下图标示的地方即可查看相应的计算机名称

9、将改好的license. lic 文件拷到你的License Manager安装目录下

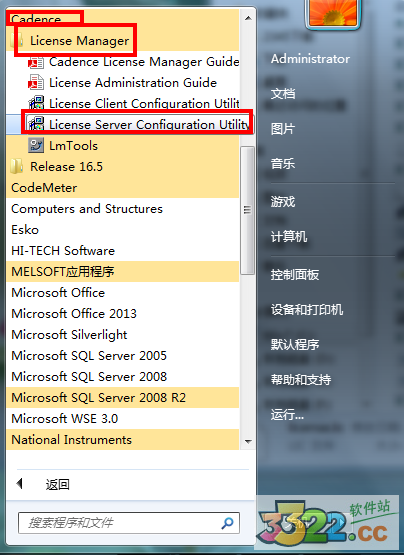

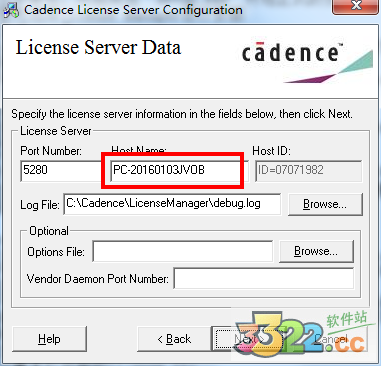

10、点击菜单,然后点击Cadence,再点击License Manager,然后选择License servers configuration Unilily将其打开

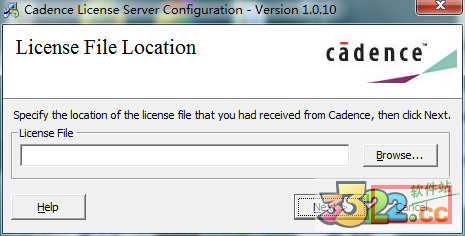

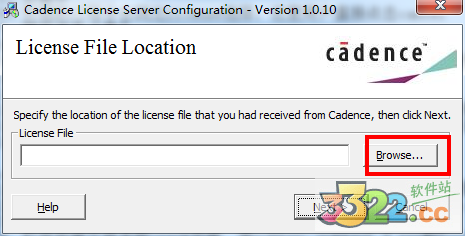

11、点击browse

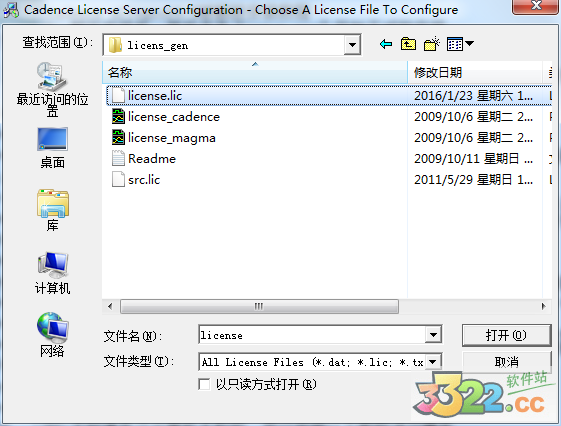

12、加载license.lic

13、点击next

14、计算机名确认之后点击staring

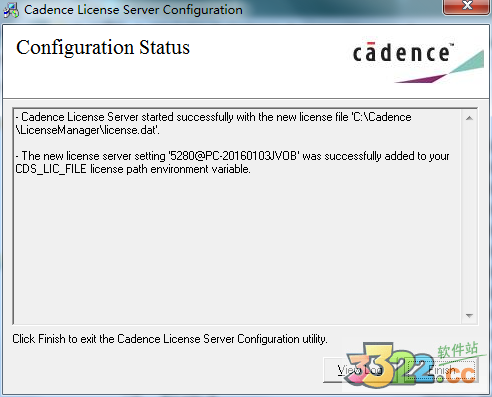

15、点击finish

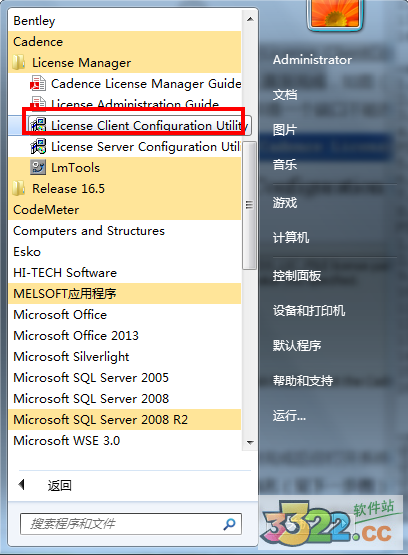

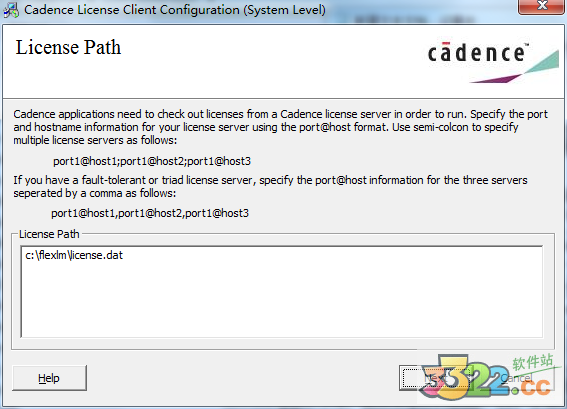

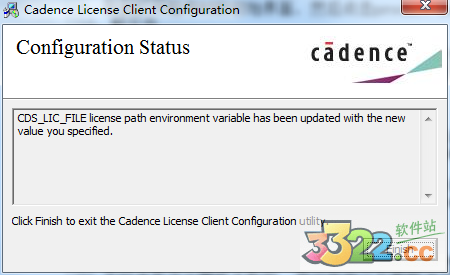

16、运行License ClientConfigurati on Utili ty,点击next

17、点击finish

18、鼠标右键点击计算机,然后点击“属性”

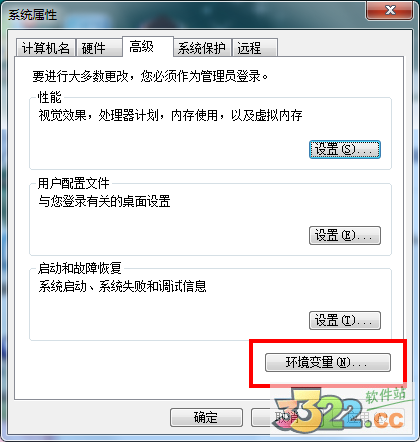

19、然后点击高级系统设置

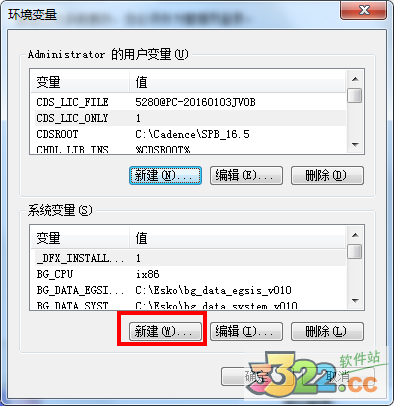

20、点击环境变量

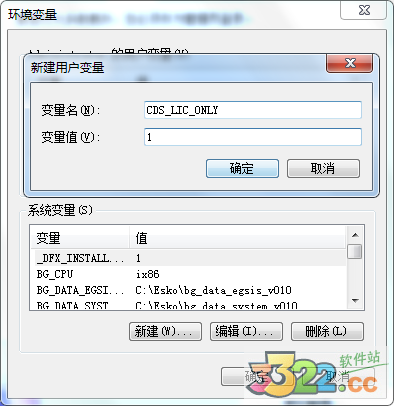

21、先选择新建用户变量,新建如下变量

CDS_LIC_FILE 变量值:5280@你的电脑名

CDS_LIC_ONLY变量值:1

22、再选择系统变量进行新建

CDS_LIC_FILE 变量值:5280@你的电脑名

CDS_LIC_ONLY变量值:1

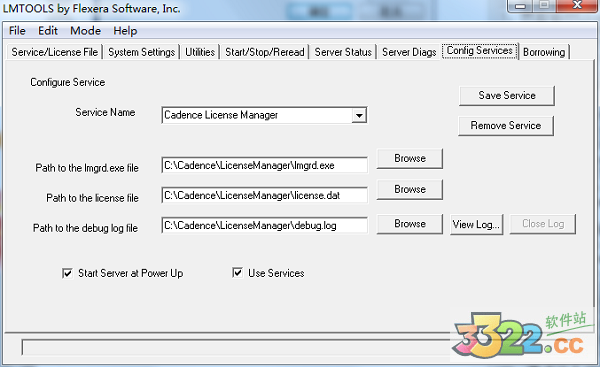

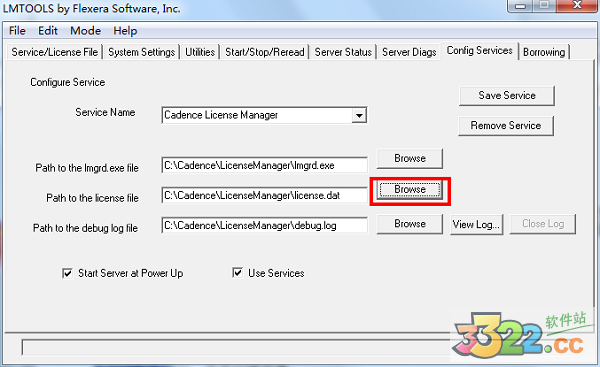

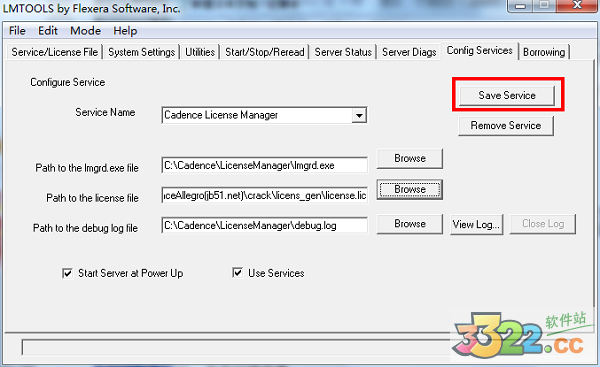

23、运行LMtools选择ConfigSerices

24、第2个路径(path to license file)单击Browse添加证书,将License.bat换成知识兔生成的License.lic,然后点击save service

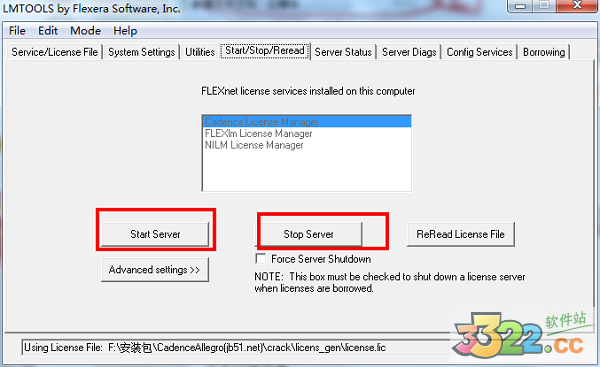

25、单击Start/Stop/Reread栏,见下图先单击Stop Servi ce停止服务,在单击Start Service。

26、现在记得要在 第八步 把安装目录下的 SPB_16.5/tools/pspice 目录下剪切出来的 orsimsetup.dll 放回原位 (如果不用仿真部分删掉也无所谓)破解完成

16.5破解版功能与特点

设计分割

设计团队越来越分散于世界各地,这就让缩短设计周期时间的相关问题变得更加复杂,手动操作解决多用户问题非常耗时, 缓慢而且易于出错,PCB设计分割技术, Allegro PCB设计层有分享,分享了多用户, 同步的设计方法,实现了更快地上市,并减少了布局时间,使用该技术,同时作业于一个布局图的多个设计师可以共同调用单个数据库,不管小组相隔多远,设计分割技术让设计师能够将设计分割为多个部分或者区域,由多个设计组成员进行规划和编辑, 这样,所有设计师都可以查看所有被分割的部分,并更新设计视窗,监控其他用户部分的状态和进度,这可以大大缩短整个设计周期,并加速设计流程。

交互式走线编辑

PCB编辑器的交互式布线功能分享了强大的,交互的功能,可以使受控自动操作,以维持用户操作,同时将布线效率最大化,实时的,图形的,任意角度的推挤布线让用户可以选择,推挤优先,,环绕优先,或,仅环绕,模式,推挤优先模式让用户可以建造最合适的互联路径,而实时的,图形布线器会自动地解决动态推挤障碍,布线会自动跳跃障碍,如引脚或导孔,在需要建造数据总线时,贴线优先模式是完美的解决方案,在环绕优先模式中,布线器图形会跟随其它互联为优先,只有在没有选择的时候才会推开或跳过障碍,仅环绕型执行起来就像环绕优先模式,但没有对其它蚀刻目标的推挤意图,实时嵌入式图形布线引擎可以通过推挤障碍,或者跟随铜皮的障碍,同时动态地跳跃过孔或元件引脚以优化布线,在编辑时,设计师可以使用一种能够显示具有高速约束的互联下的时序间隙的实时图形化窗口,互联布线还分享了在多个线路上执行群组布线的能力,以及用高速长度或延迟约束进行线路的交互式调整的能力

动态铺铜

动态铺铜技术分享了实时灌注/修复功能, Shape参数可以被适用于三个不同的方面, 参数可以被添加到全局Shape, 同类Shape, 以及单个Shape中,走线,导孔和元件添加到动态铜皮中,将会按照其形状自动连接或避让,当物体被移去时,形状会自动填充回去,在编辑完成后,动态铺铜不需要批量自动避让,也不需要其它的后期加工步骤, RF设计RF设计要求包括要比以往更快,更精确地解决高性能/高频率电路,RF/复合信号技术为PCB RF设计分享了一种完整的,从前端到后端,从原理图到布局到制造的解决方案,RF技术包含了高级的RF性能,包括参数化创建和编辑RF器件的智能布局功能, 以及一种灵活的图形编辑器,一种双向的IFF界面分享了RF电路数据的快速而有效地传输,并进行仿真和确认,这种双向流程消除了电路仿真和布局之间手动和易于出错的迭代,Allegro PCB Design XL和GXL级分享了此功能

PCB制造

可以进行全套底片加工,裸板装配和测试输出,包括各种格式的Gerber 274x,NC Drill和裸板测试,更重要的是,CADENCE通过其Valor ODB++界面,还包含Valor Universal Viewer,支持业界倡导的Gerber-Less制造, ODB++数据格式可创建精确而可靠的制造数据,进行高质量的Gerber-Less制造

自动化的互联环境

设计复杂度,密度和高速布线约束的提高使PCB的手动布线既困难又耗时,复杂的互联布线问题通过强大的,自动化的技术得以解决,这种强大的,经实践证明的自动布线器含有一种批量布线模式,含有众多的用户可定义的布线策略,以及自动的策略调整,互动的布线环境,具有实时互动走线推挤特性,有助于对走线的快速编辑,具有广泛的布图规划功能和完整的元件放置特点的互动式放置环境,使得无需切换应用程序就可以进行放置变更,优化布线,通过使用自动交互式布图规划和放置功能,设计师可以提高布线质量和效率,这与元件布局直接相关,此外,广泛的规则集让设计师可以控制范围广泛的约束,从默认的板级规则到按照线路种类的规则,再到区域规则,Allegro产品分享的高速布线能力能够解决线路安排,时序,串扰,布线层的设置,和当今高速电路所需要的特殊器件要求。

自动布线

高级自动布线技术分享了强大的,基于形状的自动布线,有快速,高效率等特点,它的布线算法可对于类型广泛的PCB互连挑战,从简单到复杂,从低密度到高密度,并可满足高速约束的需要,这些强大的算法最高效率地使用了布线区域,为了给各种情形找到最佳的布线方案,布线器使用一种多通路,重视成本,可解决冲突的算法,广泛的规则集分享了物理和电子约束控制的能力,广泛的规则集具有解决设计中各种布线元素的特定规则的灵活性,用户可以定义满足通用物理/间距线路规则所需的规则,和复杂,层级高速规则的分类规则

可制造性设计

制造性设计能力可以大大提高制造的良品率,制造算法分享了伸展功能,能够根据可用空间自动地加大铜皮间隙,自动铜皮伸展,将铜皮重新定位,创造铜皮与引脚,铜皮与SMD焊盘,以及相邻铜皮之间的额外空间,从而提高可制造性,用户可以灵活地定义各种范围的间距值,或者使用默认值, 临近的拐角和测试点可以被添加到布线过程中,制造算法会自动使用最优的规则范围,从最大值开始直到最小值,测试点插入可自动添加到可以测试的导孔或焊盘作为测试点,可测试的导孔可以在前端,后端或PCB的两边被探测到,支持单面和蛤壳式测试器,设计师可以根据它们的制造需要,灵活选择测试点插入方法,为了避免昂贵的测试设备调整,测试点可以是,固定,的,测试点约束包括测试探测表面,导孔尺寸,导孔栅格,和最小的中心间距。

互动式布线编辑

布线编辑器可以简化走线编辑过程,随着新的走线,推挤功能会自动推开原有的走线,围绕引脚进行布线,使用推挤功能,设计师可以沿着现有的走线移动原有的走线部分或导孔,并且在必要的时候推到其它引脚和导孔前端,重像功能使其更容易评估假定的情况,随着走线部分或导孔在指针控制下移动,周围的走线就会被推挤和动态显示,这样经调整的布线可以在接收最终配置前被评估,布线编辑器非常适合密集的多层电路板,有效导孔的位置很难发现,只要在选定的地点点击两次就可以定位导孔,可能的话,可以通过将走线推挤到所需的板层上创造出可选地点,如果不可行,布线编辑器会显示出DRC,并显示附近的有效导孔位置,此外,复制布线功能可以让现有的布线被复制,以完成未布线的总线连接,简化总线的创建。

布局编辑

布局编辑器让设计师迅速放置元件的同时可以同步评估空间,逻辑流程和拥挤度,移动模式让元件可以被作为单一元件或群组进行翻转,旋转,排列,推挤和移动,指导布局模式选择具有最高连通性的元件,计算出其最理想的位置,而不会破坏设计规则或约束,用户可以拒绝也可以接受该位置, 只要直接输入XY轴位置就可以放置元件, 这种功能对于放置连接器和有固定位置的元件特别实用,密度分析可以通过将PCB与显示区域范围的色图,从高度拥挤到轻微拥挤的区域,重叠,图形化地显示了电路的拥挤度,这有助于确认在哪里进行布局调整,以缓解拥挤度,并提高布线完成率

高速约束

高速布线约束和算法能够满足当今高速电路的差分对,线路布局,时序,串扰,布线层的设置和特殊的几何要求,对于差分对布线,用户只需定义两个走线之间的间距,而自动布线器会解决剩下的一切,布线算法可以智能地处理导孔周围或之间的布线, 并自动顺应指定的长度或时序标准,自动网络屏蔽被用于降低噪声敏感型线路中存在的干扰,不同的设计规则可以被应用于设计的不同部分,例如,用户可以在设计的走线部分指定严格的间距规则,而在其它地方指定没那么严格的规则。

PCB编辑器集成

PCB布线技术被紧密结合到PCB编辑器中, 通过PCB编辑器界面,所有设计信息和约束被自动传递到布线器,一旦布线完成,所有布线信息会自动传回到PCB编辑器, 图6,布局编辑器容许你在布线过程的所有阶段评估空间,逻辑流程和拥挤度。

特别说明

如果运行“ToolsPubkey.bat”文件出现can not open或者是 diff pubkey等字样时不必惊慌,文件还是能够破解的,继续运行,详细方法请参照安装教程。

下载体验